Chapter 6 Pipelining(1)

Chapter 6 Pipelining(1)

目录中英对照表

| 章节编号 | 英文标题 | 中文标题 |

|---|---|---|

| 6.1 | Basic Concept of Pipelining | 流水线的基本概念 |

| 6.2 | Pipeline Organization | 流水线的组织结构 |

| 6.3 | Pipeline Issues | 流水线中的问题 |

| 6.4 | Data Dependencies | 数据相关性 |

| 6.5 | Memory Delays | 内存延迟 |

| 6.6 | Branch Delays | 分支延迟 |

| 6.7 | Resource Limitations | 资源限制 |

| 序号 | 英文标题 | 中文标题 |

|---|---|---|

| 1 | Making the Execution of Programs Faster | 提高程序执行速度 |

| 2 | What is Pipelining? | 什么是流水线? |

| 3 | Car Assembly Line Example | 汽车装配线示例 |

| 4 | Pipelining a Processor | 对处理器进行流水线处理 |

| 5 | Pipeline Terminology | 流水线术语 |

| 6 | Pipeline Organization | 流水线的组织结构 |

提高程序执行速度的两种方法

- 使用更快的电路技术: 使用更先进的电路技术来构建处理器和主存,从而加快数据处理和存取速度。

- 硬件并行操作: 通过重新组织硬件,使得多个操作能够同时进行(并行处理)。

关键点:

- 核心思想:虽然完成单个操作所需的时间没有变化,但通过并行化的方式,可以在相同时间内完成更多的操作,从而显著提高每秒执行的操作数量(操作吞吐量)。

什么是流水线(Pipelining)?

- 定义: 流水线是一种用于构建高速处理器的关键实现技术。它通过使多条指令的执行在时间上重叠,从而提高处理效率。

- 核心思想: 让多条指令的执行重叠,以充分利用硬件资源。

- 本质: 在上一条指令尚未完成执行时,启动下一条指令的执行。

总结:

- 流水线的目标是通过任务分阶段处理,将多个操作交错执行,从而在相同时间内完成更多工作,提高系统的吞吐量。

汽车装配线示例

1. 流水线与处理器流水线的类比

- 汽车装配线与处理器流水线类似,任务被分解为多个步骤,每个步骤由独立的“站”负责完成。

- 假设汽车装配线有四个站点,每个站点执行以下任务:

- 准备汽车底盘

- 安装车身

- 安装发动机

- 安装其他部件

- 准备汽车底盘

- 简化假设:每个任务需要 1 小时。

2. 两种生产模式比较

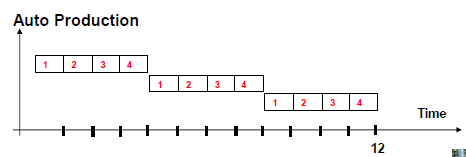

(1) 顺序生产模式(Sequential Auto Production)

- 每辆车必须依次完成四个步骤,下一辆车只能在前一辆车完成后才开始生产。

- 如果生产 4 辆汽车,总时间 = 4 辆车 × 4 小时/辆 = 16 小时。

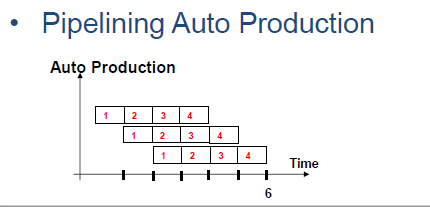

(2) 流水线生产模式(Pipelining Auto Production)

- 每辆车的每个步骤由不同站点并行完成:

- 第一小时:站点 1 完成第 1 辆车的底盘准备。

- 第二小时:站点 1 开始第 2 辆车,站点 2 开始第 1

辆车的车身安装,依此类推。

- 第一小时:站点 1 完成第 1 辆车的底盘准备。

- 从第 4 小时开始,每小时可完成一辆车。

- 总时间 = 4 小时(填满流水线) + 3 小时(剩余汽车完成) = 7 小时。

3. 关键点

- 顺序生产:处理一个任务需要较长时间,总时间与任务数成正比。

- 流水线生产:通过任务分解和并行处理,总时间大幅减少,显著提高效率。

4. 结论

- 流水线的优势在于重叠多个任务的执行,增加吞吐量,减少总完成时间。

处理器流水线(Pipelining a Processor)

1. 指令执行的五个步骤(回顾 Figure 5.4):

- 1. 指令获取(Instruction Fetch):从内存中获取指令并递增程序计数器(PC)。

- 2. 指令解码和寄存器读取(Instruction Decode and Register Read):解码指令并从寄存器文件读取操作数。

- 3. 执行操作或计算地址(Execution operation or calculate address):执行 ALU 运算或计算内存地址。

- 4. 内存访问(Memory Access):读取或写入内存数据。

- 5. 写回结果(Write result into register):将结果写入目标寄存器。

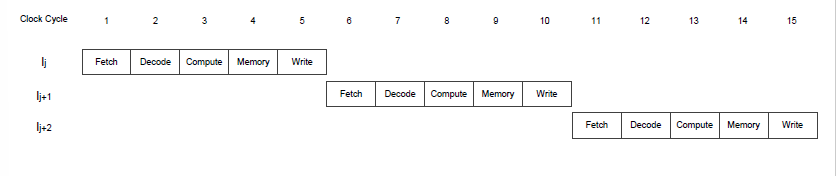

2. 非流水线执行(Unpipelined Execution):

- 在非流水线的处理器中,指令必须逐步完成所有五个阶段,且每次仅处理一条指令。

- 执行多个指令时,每条指令依次执行以下步骤:

- 第一条指令

(Ij):依次经历取指、解码、计算、内存访问、写回(需要 5

个时钟周期)。

- 第二条指令

(Ij+1):只有在第一条指令完全完成后才开始执行,再次需要 5

个时钟周期。

- 例如,执行三条指令需要 15 个时钟周期。

- 第一条指令

(Ij):依次经历取指、解码、计算、内存访问、写回(需要 5

个时钟周期)。

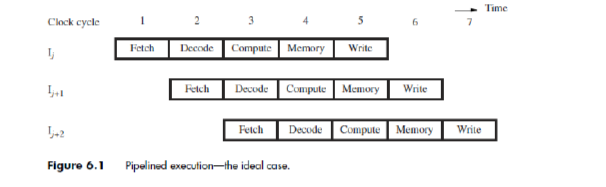

3. 流水线执行(Pipelined Execution):理想情况:

- 每个阶段 1 个时钟周期:每条指令的每个阶段都在 1 个时钟周期内完成。

- 并行处理:处理器每个时钟周期都可以接收一条新指令。

- 阶段重叠:指令分阶段执行时,多个指令可以在不同的阶段同时处理。例如:

- 时钟周期 1:第 1 条指令取指。

- 时钟周期 2:第 1 条指令解码,第 2 条指令取指。

- 时钟周期 3:第 1 条指令执行,第 2 条解码,第 3 条取指。

- 依次类推,流水线填满后每个时钟周期可以完成一条指令。

4. 关键点:

- 非流水线模式:一次只能完成一条指令,效率低。

- 流水线模式:通过阶段重叠,显著提高处理器吞吐量。尽管单条指令的完成时间(延迟)没有变化,但在流水线填满后,每个时钟周期都可以完成一条新指令,极大提高了效率。

流水线术语(Pipelining Terminology)

1. 流水线阶段(Pipe Stage / Pipe Segment)

- 定义:流水线完成指令的一步操作。

- 说明:每个阶段对应指令执行的一个步骤,例如取指、解码、执行、内存访问或写回。

2. 流水线深度(Pipeline Depth)

- 定义:流水线中阶段的数量。

- 说明:处理器流水线的深度通常由设计决定,例如 5 阶段流水线(对应指令的五个执行步骤)。

3. 延迟(Latency)

- 定义:单条指令从进入流水线到完成所需的时间。

- 说明:即单条指令经过所有阶段所需的时钟周期数。

- 特性:即使流水线能够重叠多个指令执行,单条指令的延迟仍然等于流水线的深度。

4. 吞吐量(Throughput)

- 定义:单位时间内完成的指令数量(每秒完成的指令数)。

- 说明:吞吐量是流水线效率的重要衡量指标,受限于硬件资源和数据依赖。

- 特点:

- 理想情况下,当流水线填满后,吞吐量接近每个时钟周期完成一条指令。

- 吞吐量与延迟无直接关系,而是依赖于流水线阶段的并行性。

- 理想情况下,当流水线填满后,吞吐量接近每个时钟周期完成一条指令。

总结:

- 流水线阶段:流水线的基本单元,每一步完成指令的一部分工作。

- 深度:流水线的分解程度,通常越深的流水线可以支持更高的指令并行性。

- 延迟:完成单条指令所需的总时间。

- 吞吐量:每秒完成的指令数量,流水线优化的主要目标是最大化吞吐量。

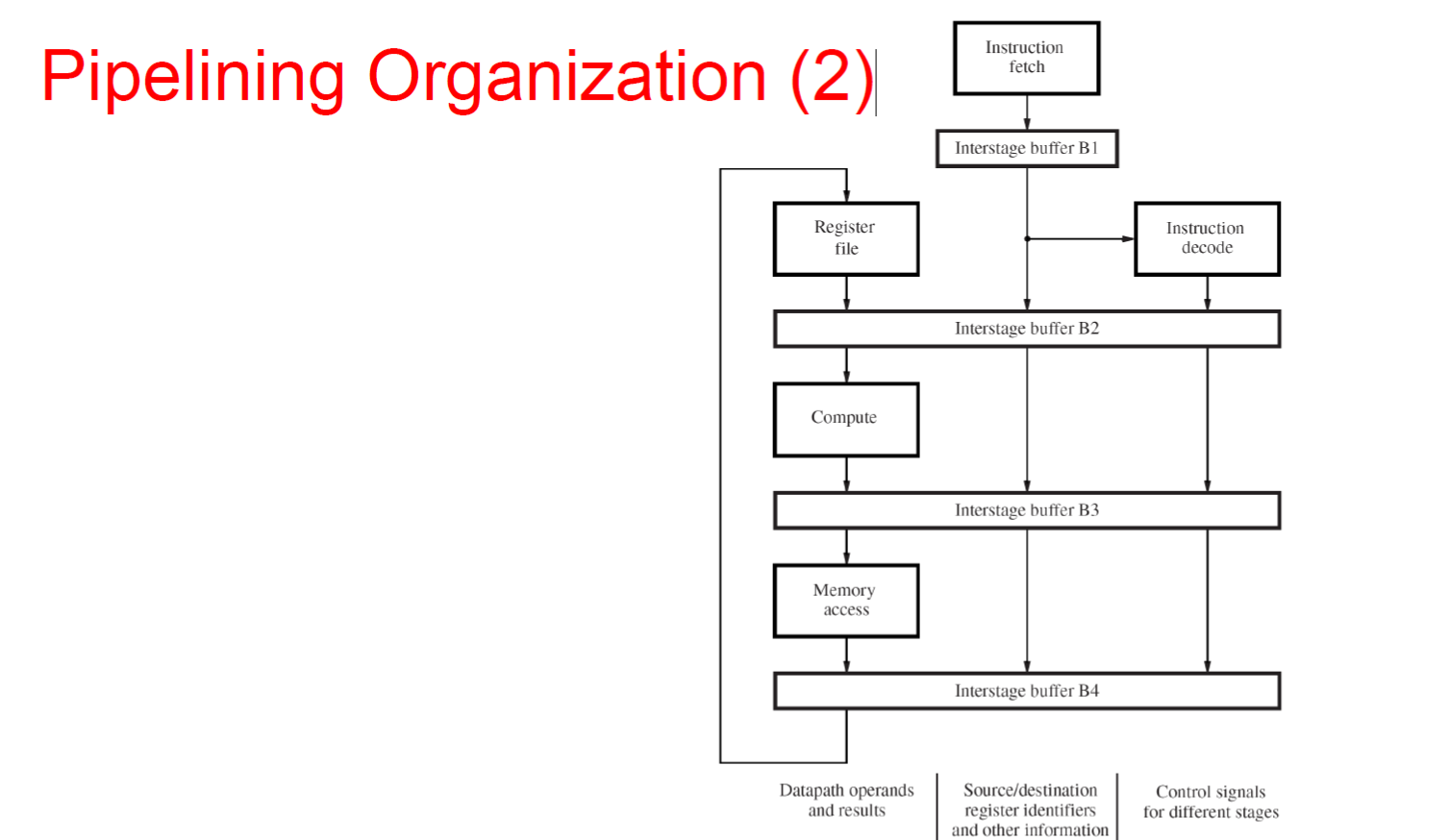

流水线的组织结构(Pipelining Organization)

1. 使用程序计数器 (PC) 获取指令

- 程序计数器 (PC):指向当前需要执行的指令地址。

- 流水线在每个时钟周期获取一条新指令,并将其送入流水线的第一个阶段。

2. 流水线的基本流程

- 每个时钟周期都有新指令进入流水线。

- 指令在流水线的各个阶段之间流动时,需要携带指令特定的信息(例如操作数和控制信号)。

3. 阶段间缓冲区(Interstage Buffers)

- 作用:用于存储指令在不同阶段流动时所需的信息。

- 包含内容:

- 寄存器:从第 5 章提到的 RA、RB、RM、RY、RZ、IR 和

PC Temp。

- RA / RB:源寄存器内容。

- RM:存储器操作数。

- RY / RZ:ALU 运算结果。

- IR:指令寄存器,用于存储当前指令。

- PC Temp:临时存储程序计数器值。

- 控制信号设置:缓冲区还需要保存指令执行过程中需要的控制信号。

- 寄存器:从第 5 章提到的 RA、RB、RM、RY、RZ、IR 和

PC Temp。

精华:

- 流水线组织的关键点:通过阶段间缓冲区(Interstage

Buffers)存储指令相关数据,确保指令流在各阶段顺畅传递。

- 目标:最大化流水线的利用率,保证多个指令的同时执行和阶段信息的完整性。

全篇总结

- 流水线不降低指令的延迟(Latency)

- 每条指令的完成时间并没有减少。

- 单条指令依然需要经过所有流水线阶段,所需时间保持不变。

- 每条指令的完成时间并没有减少。

- 流水线减少每条指令的平均执行时间

- 通过重叠多个指令的执行步骤,流水线在单位时间内处理更多指令。

- 平均每条指令的执行时间被有效分摊。

- 通过重叠多个指令的执行步骤,流水线在单位时间内处理更多指令。

- 流水线提高了整体吞吐量(Throughput)

- 单位时间内完成的指令总数增加。

- 这是流水线优化的核心目标。

- 单位时间内完成的指令总数增加。

测验题及答案解析

1. 在典型的五级 CPU 流水线中,第一个阶段是?

选项:

A. Fetch(取指)

B. Decode(解码)

C. Compute(计算)

D. Write(写回)答案:A. Fetch(取指)

解析:五级流水线的第一个阶段是从内存中获取指令(取指阶段),然后依次是解码、计算、内存访问和写回阶段。

2. 当程序执行时多条指令重叠执行时,这种功能称为 ____。

选项:

A. Multitasking(多任务处理)

B. Multiprogramming(多程序处理)

C. Hardwired control(硬连线控制)

D. Pipelining(流水线)答案:D. Pipelining(流水线)

解析:流水线是一种通过将多条指令的执行步骤重叠在时间上并行处理的技术,以提高处理器的吞吐量。

3. 判断题:流水线通过减少指令的执行时间来提高处理器性能。

- 答案:False(错误)

解析:流水线不减少单条指令的执行时间(延迟),而是通过阶段重叠提高指令的吞吐量,从而整体提高处理器性能。

- 五级流水线的第一个阶段是取指(Fetch)。

- 指令重叠执行的功能称为流水线(Pipelining)。

- 流水线提高的是整体吞吐量,而不是减少单条指令的执行时间。

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 Totoroの旅!

评论