Chapter 8 Cache(3)

Chapter 8 Cache(3)

这一节是讲解DRAM。

Contents of this Lecture

| 中文 | English |

|---|---|

| 动态随机存取存储器单元 (DRAM) | Dynamic RAM Cell |

| 动态随机存取存储器芯片的组织 | Organization of Dynamic RAM Chips |

| 同步动态随机存取存储器 (SDRAM) | Synchronous DRAM |

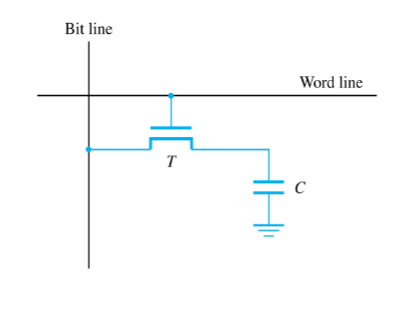

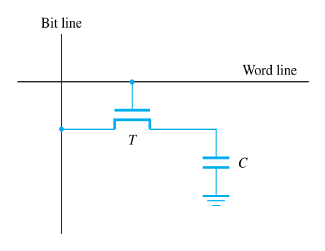

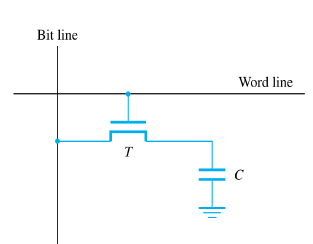

动态随机存取存储器(DRAM)单元

(1)

- DRAM单元的实现

- 信息以电容C上的电荷形式存储。

(2)

- 读操作

- 当字线为高电平时进行读取。

- 读取“1”:如果电容上存储的电荷超过阈值,感应放大器将位线驱动至表示“1”的完整电压。这一电压会将电容重新充电至对应“1”的满电荷。

- 读取“0”:如果电容上的电荷低于阈值,感应放大器将位线拉至地电平,从而确保电容没有电荷,表示“0”。

(3)

- 写操作

- 当字线为高电平时进行写入。

- 写“1”:将高电压施加到位线上。

- 写“0”:将低电压施加到位线上。

- 保持状态

- 当字线为低电平时,数据保持状态。

- 刷新

- 由于存储单元存在泄漏,数据会随时间丢失,因此需要定期刷新。

(4)

- 优点

- 高密度,低成本。

- 缺点

- 访问时间较长。

- 存储有泄漏,需要定期刷新。

动态随机存取存储器(DRAM)芯片的组织

(1)

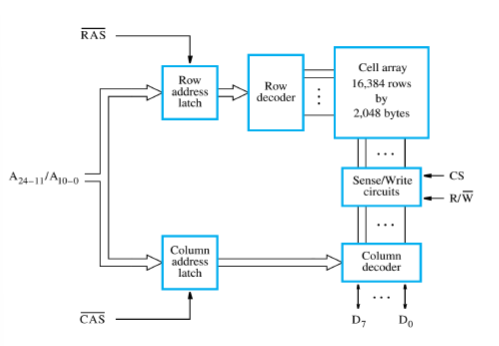

- 256M位单元的组织 (32M × 8)

- 需要 14位地址 来选择一行(Row)。

- 另需 11位地址 来指定选中行中的8位数据。

- 总共 需要 25位地址。

理解 256M位单元的组织 (32M × 8) 需要分成两部分:

- 行地址选择(14位地址):

- 总共有 32M(32,768,000) 个存储单元(行),所以需要14位地址来选择一个行(因为 $ 2^{14} = 16,384 $,而32M的行数在14位地址的范围内)。

- 这14位地址用于选择不同的行。

- 列地址选择(11位地址):

- 每行有 8位数据,也就是每行有8个存储单元。为了指定某一行中的具体8个单元,另外需要 11位地址 来选择列(因为 $ 2^{11} = 2048 $,每行有2048列数据)。

- 这11位地址用于选择一个具体的列,来读取或写入一组数据(每组8位数据)。

(2)

- 256M位单元的组织 (32M × 8)

- 为了减少外部连接所需的引脚数,行地址和列地址在14个引脚上进行复用。

- 行地址选通(RAS):用于选通行地址。

- 列地址选通(CAS):用于选通列地址。

同步动态随机存取存储器(SDRAM)

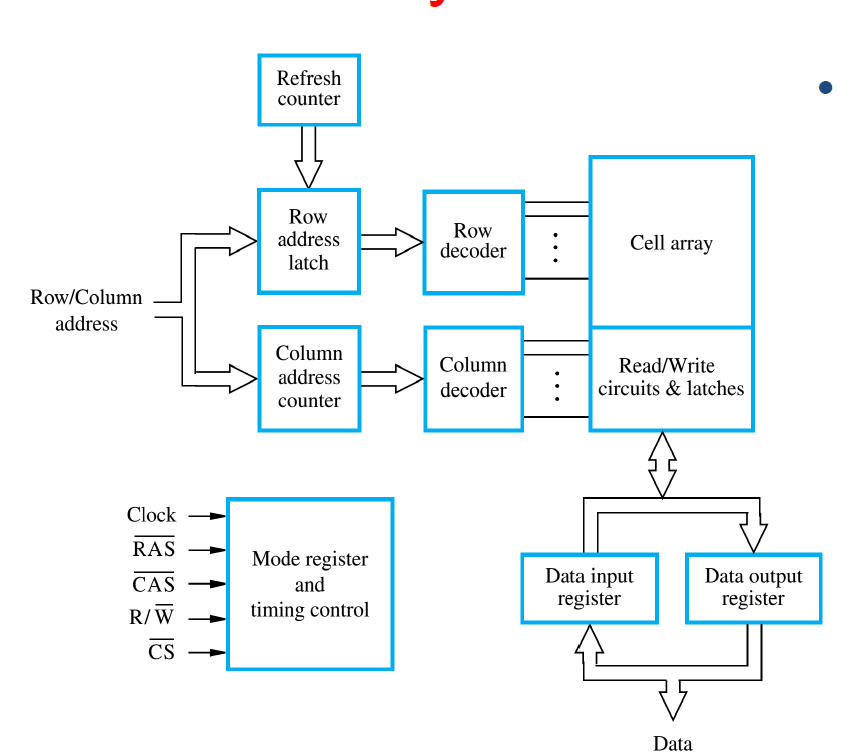

SDRAM的特点:

- 同步操作:SDRAM的操作与时钟信号直接同步,这意味着所有的读写操作都是基于时钟信号的节拍来执行的。

SDRAM芯片的结构:

- SDRAM有多个操作模式,可以通过向模式寄存器写入控制信息来选择不同的模式。

- 突发操作(Burst Operation):SDRAM利用块传输(block transfer)能力进行数据传输。在这种模式下,数据一次性传输多个列数据。

- 模式寄存器:保存12位值,SDRAM根据这些值确定在突发操作中应该传输多少列数据,以及以何种顺序传输。

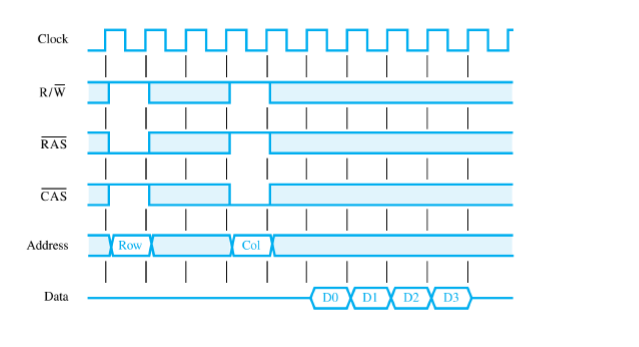

示例:SDRAM的突发读取(Burst read):

- 例如,SDRAM可以进行长度为4的突发读取,连续读取4个数据单元。

延迟和带宽:

- 延迟(Latency):表示从内存中传输一个数据字所需的时间。在块传输中,延迟指的是传输第一个数据字之前的时间。

- 带宽(Bandwidth):指的是内存每秒钟能够传输的比特数或字节数。带宽取决于存储数据的访问速度以及能够并行访问的数据位数。

- 带宽的有效值还取决于连接内存和处理器的链路的传输能力。

- 有效带宽 = 总线速度 × 总线宽度

双倍数据速率SDRAM(DDR SDRAM):

- DDR SDRAM与标准SDRAM在存取单元数组的方式上相同,但它在时钟的两个边缘进行数据传输,即每个时钟周期传输两次数据。

- 延迟:DDR SDRAM的延迟与标准SDRAM相同,但其带宽基本上在进行长时间突发传输时翻倍。

示例:

- 第一个数据字在5个时钟周期后传输。这里的延迟就是5个时钟周期。

DDR版本:

- DDR(2.5V,200~400MHz,1GB)

- DDR2(1.8V,400~800MHz,4GB)

- DDR3(1.5V,800~2400MHz,8GB)

- DDR4(1.2V,1600~3200MHz,32GB)

- DDR5(1.1V,4800~6400MHz,128GB)

这些版本表示不同电压、时钟频率和存储容量的DDR内存。

(Quiz)

问题 1:

与SRAM相比,DRAM的主要优势是 ____。 A. 高速度

B. 非易失性存储数据

C. 高密度

D. 易于控制

正确答案:C. 高密度

- 解释:DRAM的主要优势是 高密度,它能在相同的面积上存储更多的数据,相对于SRAM,DRAM的存储密度更高,因此成本较低。SRAM速度较快,但其密度较低,成本较高。

问题 2:

DRAM的优点和缺点是什么?

- 优点:

- 高密度,低成本

- 缺点:

- 较长的内存访问时间

- 存储单元易泄漏,需要定期刷新

精华

- DRAM优点:

- 高密度:可以在较小的面积上存储更多数据,相比于SRAM,存储密度高。

- 低成本:由于采用了电容存储数据,制造成本较低。

- DRAM缺点:

- 较长的内存访问时间:由于存储方式不同,DRAM的访问速度比SRAM慢。

- 存储单元易泄漏,需要刷新:由于电容会泄漏,必须定期刷新才能保持数据,否则数据会丢失。

问题 3:

某一动态 RAM 芯片,容量为 64K × 1 ,除电源线、接地线和刷新线外,该芯片的最少引脚数目应为多少?

解答过程:

- 64K = $ 2^{16} $,表示该芯片的容量为 64K 位。

- 地址线引脚数为 8:由于地址线引脚只引出一半,所以地址线的数量是 8(实际上,这里应该是 16,表示能够选择 64K 个地址的行和列地址总共需要 16 个地址位,但题目指明了只需 8 个引脚来选择行地址)。

- 数据线引脚数为 1:数据线引脚为 1(如果数据输入和数据输出是分开的,则数据线引脚数为 2)。

- R/W:该芯片有读写信号(R/W)。

- RAS 和 CAS:该芯片有行地址选通信号(RAS)和列地址选通信号(CAS)。

计算:

- 地址线引脚数:8

- 数据线引脚数:1

- 读写信号(R/W):1

- 行地址选通信号(RAS):1

- 列地址选通信号(CAS):1

引脚总数 = 8 + 1 + 1 + 1 + 1 = 12(不包括电源线、接地线和刷新线)

正确答案:12

精华

- 容量与地址线:64K容量意味着地址线需要8个引脚来选择行地址。

- 数据线:数据线引脚数为1或2,具体取决于数据输入输出是否分开。

- 控制信号:DRAM芯片通常具有读写信号(R/W)、行地址选通信号(RAS)和列地址选通信号(CAS)。

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 Totoroの旅!

评论