Chapter 8 Cache(4)

Chapter 8 Cache(4)

这一节是讲解Structure of Larger Memories的。

Contents of this lecture

| English | 中文 |

|---|---|

| Static Memory Systems | 静态存储系统 |

| How to connect a number of static memory chips to form a much larger memory? | 如何连接多个静态存储芯片,形成一个更大的内存? |

| Dynamic Memory Systems | 动态存储系统 |

| How to connect a number of dynamic memory chips to form a much larger memory? | 如何连接多个动态存储芯片,形成一个更大的内存? |

静态存储系统 (Static Memory System)

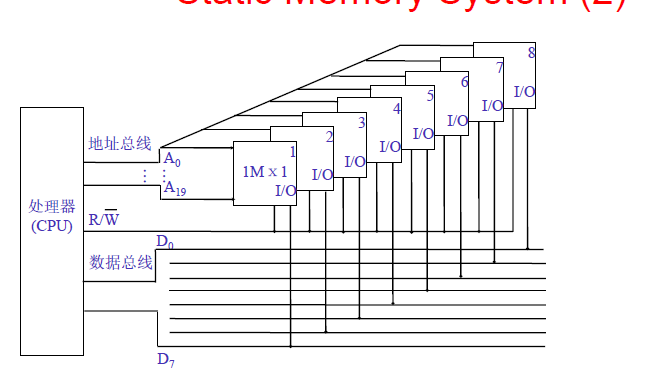

位扩展法 (Bit Expansion Method)

概念:芯片每个存储单元的位数小于存储器字长,需进行位扩展。

例子:用 1 M × 1 位存储芯片组成 1 M × 8 位存储器。

- 共需 8 片 1M × 1 位的芯片,每片存储同一位权的数据。

- 片的 I/O 端接 D₀ 到 D₇。

- 访问芯片需 20 位地址码 A₁₉ 到 A₀。

- 读写控制信号:R/W。

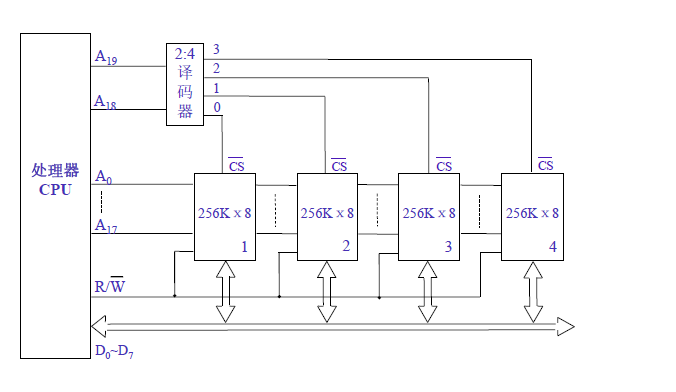

字扩展法 (Word Expansion Method)

概念:芯片每个存储单元的位数等于存储器字长,但容量不足,需进行字扩展。

例子:用 256 K × 8 位芯片组成 1 M × 8 位存储器。

- 共需 4 片 256K × 8 位的芯片(1MB / 256KB = 4)。

- 1MB 容量需 20 位地址码 A₁₉ 到 A₀,而 256KB 芯片需 18 位片内地址码 A₁₇ 到 A₀。

- 用高二位地址 A₁₉ 和 A₁₈ 经 2:4 译码器选择芯片进行读写。

- 每片 8 条 I/O 线分别接 D₇ 到 D₀。

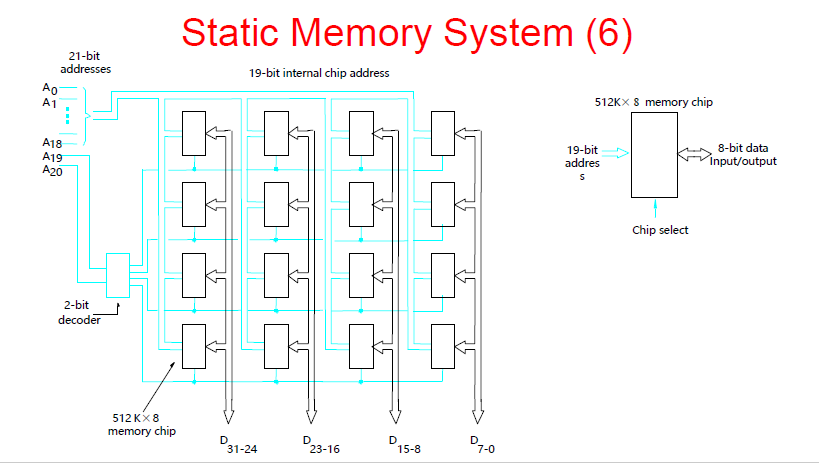

字位同时扩展法 (Word and Bit Expansion Method)

概念:单片芯片的字数和位数均小于主存的容量要求,需进行字、位的扩展。

例子:用 512K × 8 位的存储器芯片组成 2M × 32 位的存储器。

- 共需 8 片 512K × 8 位的芯片,组成 4 × 4 的阵列。

- 2M × 32 容量需 21 位地址码 A₂₀ 到 A₀,而 512KB 芯片需 19 位片内地址码 A₁₈ 到 A₀。

- 用高二位地址 A₂₀ 和 A₁₉ 经 2:4 译码器选择一行芯片进行读写。

- 每片 8 条 I/O 线分别接 D₇ 到 D₀。

结论

- 假设内存单元的容量为 M × N 位,如果使用 l × k 位的芯片来构建,所需的芯片数量为 (M/l) × (N/k)。

这些方法帮助设计和组织更大容量的存储器,并且实现了多个存储单元的组合。

动态存储系统 (Dynamic Memory System)

- 大容量动态存储系统的组织

- 大容量动态存储系统的组织基本上与静态存储系统相同。

- 封装方式:内存模块

- 内存模块:将内存芯片组装在一个小板上,并插入计算机主板上的插槽。

- SIMM(单排内存模块,Single In-line Memory Module)

- SIMM 是一种基本的 DRAM 封装类型,适用于大多数旧系统。

- SIMM 可以是单面(只有一面有内存芯片)或双面(两面都有内存芯片)。

- 30 引脚 SIMM:1MB,8 位数据,外加 1 位奇偶校验;单面。

- 72 引脚 SIMM:1MB,4MB,16MB(单面);2MB,8MB,32MB(双面);32 位数据,外加 4 位用于奇偶校验/ECC。

- SIMM 示例

- 一个 32MB 的单排内存模块(SIMM),两个芯片控制这个 SIMM。

- DIMM(双排内存模块,Dual In-line Memory Module)

- 当前,DIMM 是内存封装的标准方式。

- DIMM 能一次传输 64 位数据。

- 常见的 DIMM 类型:

- 72 引脚、144 引脚、200 引脚 DIMM:用于 SO DIMM(小型轮廓 DIMM)。

- 168 引脚 DIMM:用于 FPM(快速页模式)DRAM,EDO(扩展数据输出)DRAM 和 SDRAM。

- 184 引脚 DIMM:用于 DDR SDRAM。

- 240 引脚 DIMM:用于 DDR2 和 DDR3 SDRAM。

- 284 引脚 DIMM:用于 DDR4 SDRAM。

- 288 引脚 DIMM:用于 DDR5 SDRAM。

- DIMM 示例

- 两种类型的 DIMM:一个 168 引脚 SDRAM 模块(顶部)和一个 184 引脚 DDR SDRAM 模块(底部)。

这些内存封装技术有助于提高内存的传输速率和容量,满足不同计算需求的需求。

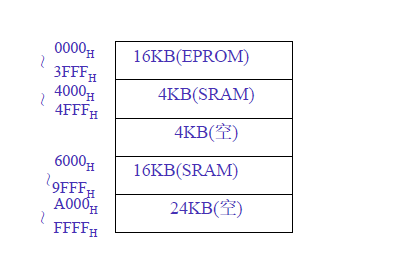

示例说明

地址总线与控制总线:

- CPU 地址总线:16根 (A15~A0),其中A0为低位。

- 双向数据总线:8根 (D7~D0)。

- 控制总线:

- MREQ:允许访存,低电平有效。

- R/W:高电平为读命令,低电平为写命令。

主存地址空间分配:

- 0000H ~ 3FFFH:系统程序区,由只读存储器(EPROM)组成。

- 4000H ~ 4FFFH:系统程序工作区,由 SRAM 组成。

- 6000H ~ 9FFFH:用户程序区,由 SRAM 组成。

- 地址空间按字节编址。

存储器芯片:

- EPROM:8K × 8 位,控制端只有 CS(片选信号)。

- SRAM:有多种容量配置:

- 16K × 1 位

- 2K × 8 位

- 4K × 8 位

- 8K × 8 位

主存设计:

- 从上述存储器芯片中选择合适的芯片设计计算机主存储器。

- 需要绘制 主存储器逻辑框图,并设计 选片逻辑,可选用门电路及 3:8 译码器(如 74 LS138),连接到 CPU。

主存地址空间:

- 0000H ~ 3FFFH:16KB 的 EPROM 存储。

- 4000H ~ 4FFFH:4KB 的 SRAM 存储。

- 6000H ~ 9FFFH:16KB 的 SRAM 存储。

存储器选用与片选逻辑:

- EPROM:可以选择 1片 8K × 8 位 EPROM 存储器,覆盖 0000H ~ 3FFFH 的地址区。

- SRAM:

- 2片 8K × 8 位 SRAM,分别覆盖 4000H ~ 4FFFH 和 6000H ~ 9FFFH 的地址区。

- 选片逻辑:使用 3:8 译码器(74 LS138),根据地址选择相应的存储器片。

通过合理的选片逻辑,将上述存储器芯片合理地分配到主存的不同区域,确保每个存储区域都能访问到正确的存储器。

Quiz

问题 1:

考虑使用 512K × 16 存储芯片构建 16M × 128 内存。需要多少行存储芯片?

解析:

- 总内存容量:16M × 128

- 每个芯片容量:512K × 16

- 所需的行数 = 总容量 / 每个芯片的容量 $ 16M / 512K = 32 $

- 答案:C. 32

问题 2:

考虑使用 512K × 8 存储芯片构建 64M × 16 内存。需要多少个存储芯片?

解析:

- 总内存容量:64M × 16

- 每个芯片容量:512K × 8

- 所需的存储芯片数量 = 总容量 / 每个芯片的容量 $ (64M × 16) / (512K × 8) = 256 $

- 答案:D. 256

问题 3:

假设一个内存可以使用 20 位地址访问,其字长为 64 位,并且是按字寻址的。假设我们使用 256K × 8 位的 SRAM 芯片来构成这个内存。

1. 该内存能存储多少字节?

- 总地址空间:$ 2^{20} $

- 字长:64 位 = 8 字节

- 因为是按字寻址,所以总存储容量 = $ 2^{20} $ $ = 2^{20} = 8 $

答案:该内存可以存储 8 MB。

2. 需要多少个 SRAM 芯片?

- 每个 SRAM 芯片的存储容量:$ 256K = 256K $

- 总存储容量:8 MB = $ 8 $

- 需要的芯片数量 = 总存储容量 / 每个芯片的存储容量 $ 8 / 256 = 32 $

答案:需要 32 片 SRAM 芯片。

3. 需要多少地址引脚进行芯片选择?为什么?

- 每片 SRAM 芯片的地址位数:18 位地址(对应于 256K 存储单元)

- 总地址位数:20 位地址

- 低 18 位地址直接接芯片的 18 位地址端,高 2 位地址通过 2:4 译码器来选择芯片。

- 需要 2 位 地址引脚来进行芯片选择。

答案:需要 2 个地址引脚来进行芯片选择。

4. 画出使用 256K × 8 位 SRAM 芯片实现此内存的图形结构。

这个问题需要绘制图形,您可以通过如下方式理解:

- 20 位地址中的低 18 位连接到每片 SRAM 芯片的地址端。

- 高 2 位地址通过 2:4 译码器来选择芯片。

- 数据线连接到所有 32 片 SRAM 芯片的相应端口。

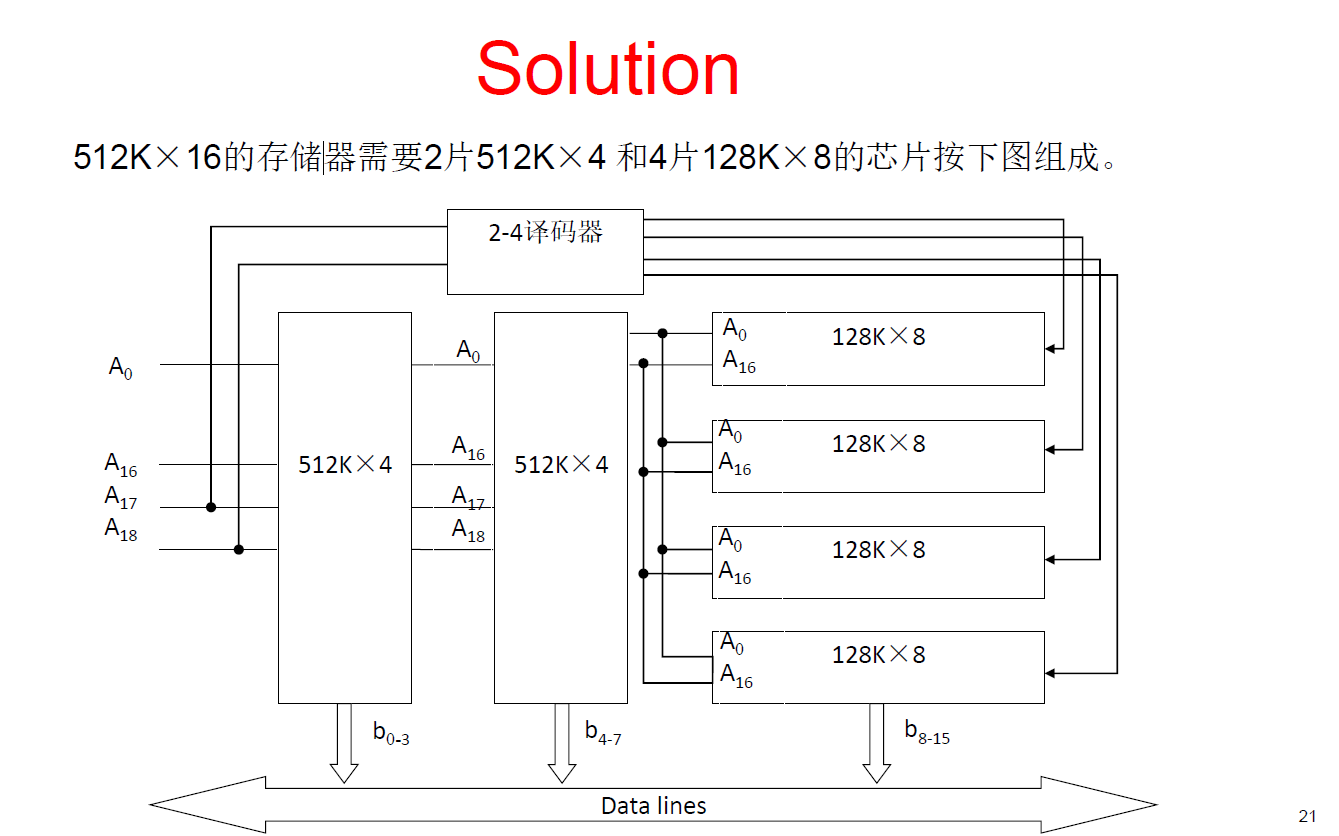

问题 4:

假设有两种类型的静态存储芯片:128K × 8 位(共 4 片)和 512K × 4 位(共 2 片)。请使用这些内存芯片实现一个 512K × 16 位的内存,并画出该内存的组织结构图。

做会这道题,这一节的知识点你就掌握了。

解决方案:

为了构建一个 512K × 16 位的内存,我们可以按以下方式组合芯片:

- 需要 2 片 512K × 4 位的芯片,和 4 片 128K × 8 位的芯片。

- 每片 512K × 4 位芯片可以提供 4 位的数据宽度,而每片 128K × 8 位芯片可以提供 8 位的数据宽度。

内存组织结构:

- 地址线:

- 需要 18 位地址来寻址 512K 单元。低 16 位用于访问单元的特定位置,高 2 位用于选择芯片。

- 通过 2:4 译码器来选择具体的芯片。

- 数据线:

- 通过组合 2 片 512K × 4 位芯片和 4 片 128K × 8 位芯片来实现 16 位的数据宽度。

图示(组织图):

- 两片 512K × 4 位芯片:

- 这两片芯片连接到数据总线的 4 位宽度上。

- 四片 128K × 8 位芯片:

- 这四片芯片提供额外的 8 位数据宽度。

- 译码器:

- 使用 2:4 译码器将高位地址(A17, A18)连接到芯片的选择信号上。