Chapter 8 Cache(5)

Chapter 8 Cache(5)

这一节是讲解5 Memory Hierarchy的。从这个标题来看,这一节的内容会比较概念,不是很重要,开始!😎

(Contents of this Lecture)

为什么需要内存层次结构?

Why Have a Memory Hierarchy?内存层次结构示例

An Example of Memory Hierarchy内存层次结构的基本思想

Fundamental Idea of the Memory Hierarchy内存层次结构如何工作?

How Does the Memory Hierarchy Work?内存层次结构设计者的四个问题

Four Questions for the Memory Hierarchy Designers

为什么需要内存层次结构? (Why Have a Memory Hierarchy?)

哪有什么是十全十美的呢?

理想内存 (Ideal Memory)

- 零访问时间 (零延迟)

- 无限容量

- 零成本

- 零访问时间 (零延迟)

问题 (The Problems)

- 理想内存的要求是相互对立的。

- 更大的内存更慢:

- 更大的内存意味着需要更长时间来确定存储位置。

- 更大的内存意味着需要更长时间来确定存储位置。

- 更快的内存更贵:

- 内存技术:SRAM 与 DRAM

- 理想内存的要求是相互对立的。

总结 (Summary)

- 我们希望内存既要快,又要大且便宜。

- 但是,单一层次的内存无法同时实现这些目标。

- 我们希望内存既要快,又要大且便宜。

思路 (Idea)

- 创建一个“快速且大”的主内存的假象。

- 使用多个存储层次 (层次越远,存储越大且越慢),确保大部分处理器需要的数据都保存在更快的内存层次中。

- 创建一个“快速且大”的主内存的假象。

内存层次结构示例

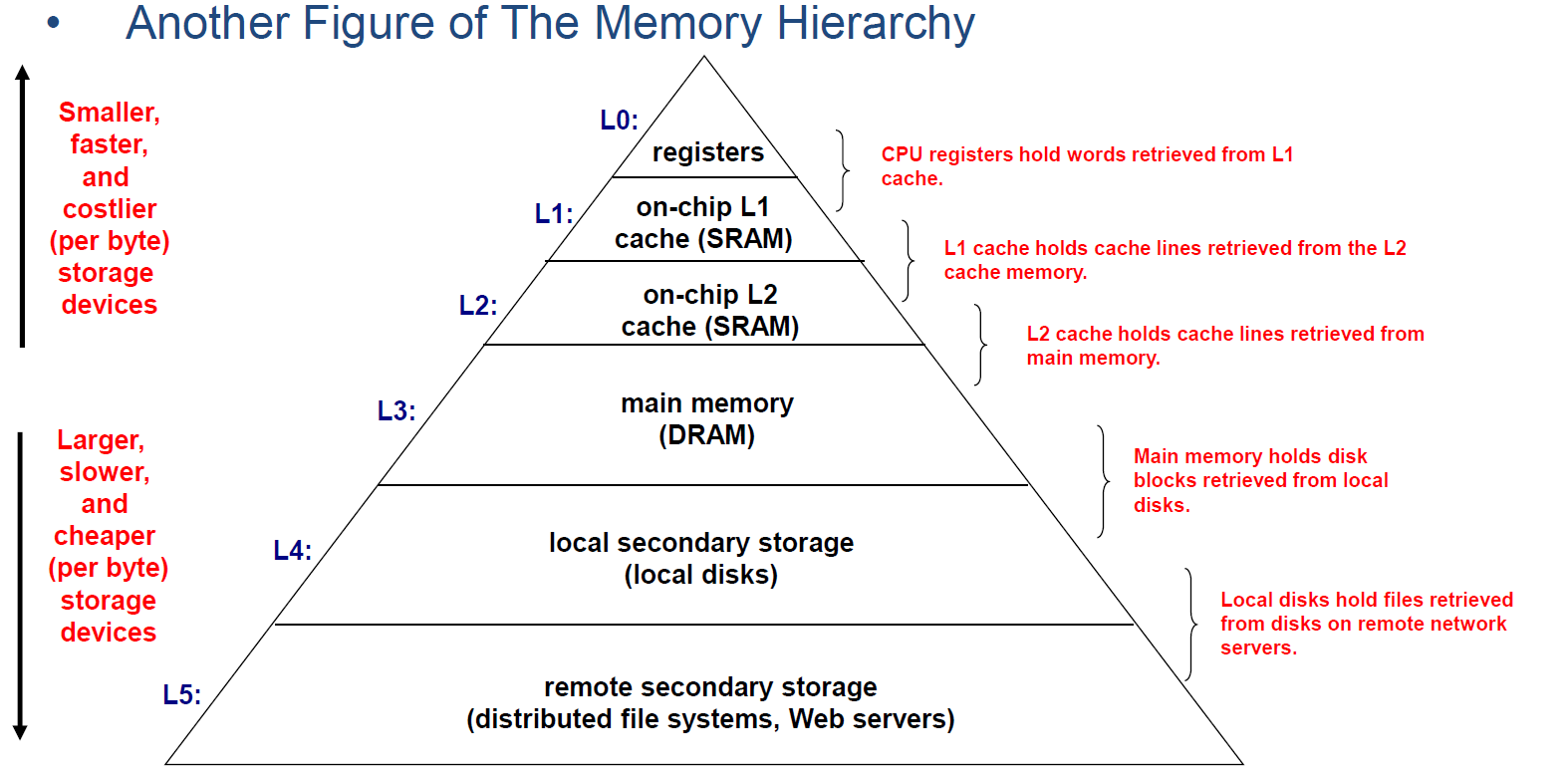

- 内存层次结构的图示 (Another Figure of The Memory Hierarchy)

- 寄存器 (Registers)

- L1缓存 (SRAM)

- L2缓存 (SRAM)

- 主内存 (DRAM)

- 本地二级存储 (Local secondary storage, local disks)

- 存储设备变得更大、更慢且每字节更便宜。

- 远程二级存储 (Remote secondary storage, distributed file systems, Web servers)

- 存储设备分类

- L0: 最小、最快、每字节成本最高的存储设备。

- L1: 更快、更小、但更昂贵。

- L2: 较大较慢,成本相对较低。

- L3: 更大、慢且便宜的存储设备。

- L4: 更大、最慢且最便宜的存储设备。

- L5: 最远且最大存储设备。

内存层次结构的基本理念

缓冲区 (Buffer)

- 缓冲区是一个较小且较快的存储设备,作为较大、较慢设备的一个暂存区,用于存储部分数据。

- 对于每个级别k,较快较小的设备在该级别作为缓冲区,用于缓存较大较慢设备k+1的数据。

- 所有数据最终都存储在最低级别的设备中。

- 数据会在相邻的两个级别之间进行复制。

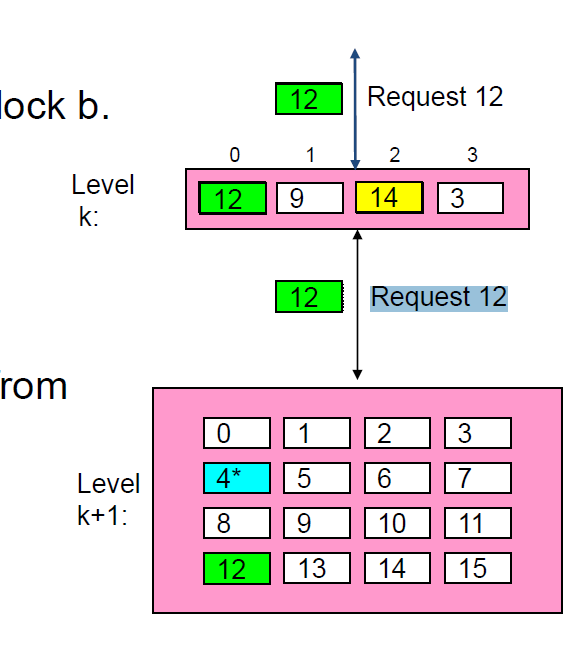

缓冲区的通用概念 (General Buffering Concepts)

- 程序需要某个对象d,而d存储在某个块b中。

- 命中 (Hit)

- 程序在级别k的缓冲区中找到了块b。

- 例如,块14。

- 程序在级别k的缓冲区中找到了块b。

- 未命中 (Miss)

- 块b不在级别k的缓冲区中,级别k的缓冲区需要从级别k+1获取它。

- 例如,块12。

- 块b不在级别k的缓冲区中,级别k的缓冲区需要从级别k+1获取它。

请求序列示例:

- 请求块14 → 缓冲区命中。

- 请求块12 → 缓冲区未命中,需要从下一级缓冲区加载。

- 各个块在缓冲区中的存放顺序和命中、未命中的情况如下图所示。

内存层次结构的工作原理

利用局部性原理

- 编写良好的程序通常具有良好的局部性。

- 程序在任何时刻通常会访问相对较小的地址空间。

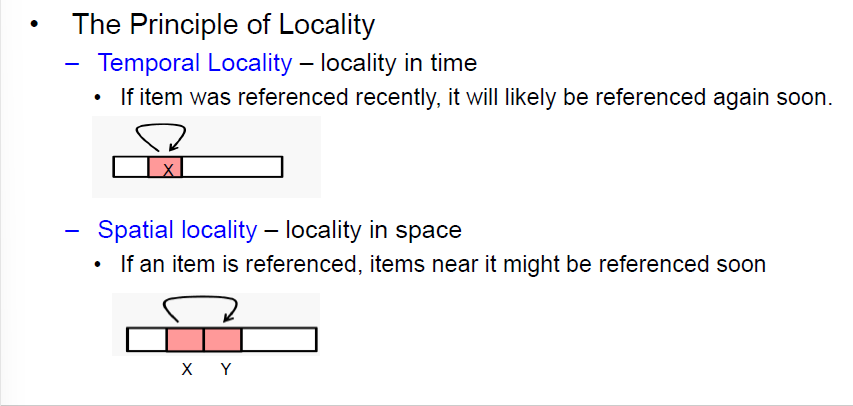

局部性原理

- 时间局部性 (Temporal Locality)

- 如果某个项最近被引用,那么它很可能会在不久后再次被引用。

- 空间局部性 (Spatial Locality)

- 如果某个项被引用,那么它附近的项可能会很快被引用。

- 时间局部性 (Temporal Locality)

在内存层次结构中的应用

- 时间局部性:

- 将最近访问的数据项保持在离处理器更近的位置。

- 空间局部性:

- 将包含连续数据的块移到更高层级的存储中。

- 时间局部性:

总结

- 程序倾向于访问级别k的数据多于访问级别k+1的数据。

- 因此,级别k+1的存储可以更慢、容量更大且更便宜。

- 效果:

- 创建一个内存池,成本接近底层便宜存储的成本,但能够以接近顶部快速存储的速度为程序提供数据。

内存层次结构设计者的四个问题

- Q1: 上层中一个块可以放置在哪里?

- 这个问题涉及到在上层存储中如何安排数据块的位置。通常,块放置的位置要考虑到存取的效率以及如何避免冲突。

- Q2: 如果块在上层,如何找到它?

- 这个问题涉及到如何高效地找到存储在上层的块。通常,采用某种形式的映射或索引来追踪块的位置,如缓存标记。

- Q3: 在缓存未命中时,应该替换哪个块?

- 这个问题涉及到替换策略。常见的替换策略有最近最少使用(LRU)、随机替换、先进先出(FIFO)等。

- Q4: 写操作时会发生什么?

- 这个问题涉及到写策略的设计。写操作可能会更新缓存、写回到下级存储,或者采用写直达存储等策略。

测验题目

存储器层次结构 _____

A. 限制程序的大小,但让它们执行得更快- 错误:存储器层次结构不会限制程序大小,它的目的是提升执行速度。

B. 是一种结构化内存分配决策的方式

- 错误:存储器层次结构主要用于提升内存访问效率,而不是内存分配的方式。

C. 利用 SRAM 的速度和磁盘的容量

- 正确:存储器层次结构利用了不同层次存储的优点,结合了 SRAM 的快速访问和磁盘的大容量,给用户提供了快速且大容量的存储体验。

D. 使得程序执行得更慢,但允许程序更大

- 错误:存储器层次结构的目的是加速程序执行,而不是使其更慢。

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 Totoroの旅!

评论